# SimpleFit: A Framework for Analyzing Design Trade-Offs in Raw Architectures

Csaba Andras Moritz, Donald Yeung, and Anant Agarwal

Abstract—The semiconductor industry roadmap projects that advances in VLSI technology will permit more than one billion transistors on a chip by the year 2010. The MIT Raw microprocessor is a proposed architecture that strives to exploit these chip-level resources by implementing thousands of tiles, each comprising a processing element and a small amount of memory, coupled by a static two-dimensional interconnect. A compiler partitions fine-grain instruction-level parallelism across the tiles and statically schedules intertile communication over the interconnect. Because Raw microprocessors fully expose their internal hardware structure to the software, they can be viewed as a gigantic FPGA with coarse-grained tiles in which software orchestrates communication over static interconnections. One open challenge in Raw architectures is to determine their optimal grain size and balance. The grain size is the area of each tile and the balance is the proportion of area in each tile devoted to memory, processing, communication, and off-chip global I/O. If the total chip area is fixed, higher processing power per tile requires large tiles and hence reduces the total number of tiles on the chip. This paper presents SimpleFit, a novel analytical framework that designers can use to reason about the design space of Raw microprocessors. Our model is also generalizable to multiprocessors on a chip. Based on an architectural model, an application model, and a VLSI cost analysis, the framework computes the performance of applications and uses an optimization process to identify designs that will execute these applications most cost-effectively. Although the optimal machine configurations obtained vary for different applications, problem sizes, and budgets, the general trends for various applications are similar. Accordingly, for the applications studied, assuming a onr billion logic transistor equivalent area, we recommend building a Raw chip with approximately 1,000 tiles, 30 words/cycle global I/O, 20 Kbytes of local memory per tile, three to four words/cycle local communication bandwidth, and single-issue processors. This configuration will give performance near the global optimum for most applications.

Index Terms—Multiprocessors, microprocessors, modeling, architecture.

# **1** INTRODUCTION

A DVANCES in semiconductor technology have made possible the integration of multiple functional units, large cache memories, reconfigurable logic arrays, and peripheral functions into single-chip microprocessors. Unfortunately, increases in the performance of contemporary microprocessors have come at the cost of increasing inefficiencies in silicon area usage. The inefficiencies arise from the complexity of designs that use hardware support to exploit more instruction level parallelism.

Maintaining a rapid increase in microprocessor performance will require a cost efficient utilization of silicon area. The MIT Raw microprocessor is a proposed architecture that exposes its internal hardware structure to the compiler so that the compiler can determine and orchestrate the best mapping of an application to the hardware. A Raw microprocessor [1] is reminiscent of a coarse-grained FPGA and comprises a replicated set of tiles coupled together by a

D. Yeung is with the Department of Electrical and Computer Engineering, University of Maryland, College Park, MD 20742.

E-mail: yeung@umiacs.umd.edu.

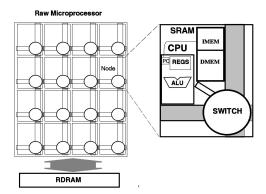

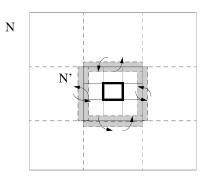

Manuscript received 11 Dec. 1998; revised 7 July 2000; accepted 25 July 2000. For information on obtaining reprints of this article, please send e-mail to: tpds@computer.org, and reference IEEECS Log Number 108432. set of compiler orchestrated, pipelined, switches (Fig. 1). Each tile contains a simple RISC-like processing core and SRAM memories for instructions and data. Instruction memory allows the multiplexing of the compute logic on a cycle by cycle basis. SRAM memory distributed across the tiles eliminates the memory bandwidth bottleneck, provides low latency to each memory module, and prevents off-chip I/O latency from limiting effective computational throughput.

The tiles are interconnected by a high-speed 2D mesh network, allowing intertile communications that are statically scheduled to occur with register-like latencies. The switches themselves contain some amount of SRAM so that the compiler can load into the switch a program that multiplexes the interconnect in a cycle by cycle fashion, just as in a virtual wires-based multi-FPGA system [4].

A typical Raw system includes a Raw microprocessor coupled with off-chip RDRAM (RamBus DRAM) through multiple high bandwidth paths. The two level memory hierarchy, namely a local SRAM memory attached to each tile inside the Raw chip and a large external RDRAM memory, is necessary to be able to solve large problems that exceed the size of the on-chip memory.

Raw architectures achieve the performance of FPGA-based custom computing engines by exploiting fine-grained parallelism and fast static communication, and by exposing the low-level hardware details to facilitate compiler orchestration. Unlike FPGA systems,

<sup>•</sup> C.A. Moritz is with the Electrical and Computer Engineering Department, University of Massachusetts, Amherst, MA 01002. E-mail: andras@ecs.umass.edu.

A. Agarwal is with the Laboratory for Computer Science, MIT, Cambridge, MA 02139. E-mail: agarwal@lcs.mit.edu.

Fig. 1. Raw system composition. A typical Raw system includes a Raw microprocessor coupled with off-chip DRAM and stream I/O devices. Each Raw tile contains a simple RISC-like processor, an SRAM memory for instructions and data, and a switch. The tiles are interconnected in a 2D mesh network that is orchestrated by the compiler. The switches themselves contain some amount of SRAM so that the compiler can load into the switch a program that multiplexes the interconnect in a cycle by cycle fashion, just as in a virtual wires-based multi-FPGA system.

however, Raw machines support instruction sequencing and are more flexible because the execution of a new operation can be accomplished merely by pointing to a new instruction. Compilation in Raw is faster than in FPGA systems because it binds into hardware commonly used to compute mechanisms, such as ALUs and memory paths, thereby eliminating repeated low-level compilations of these macro units. Binding of common mechanisms into hardware also yields better execution speed, lower area, and better power efficiency than FPGA systems.

The designer of an FPGA device or a Raw microprocessor is faced with the challenge of determining the best division of VLSI resources among computing, memory, and communication. This challenge is termed the *balance problem*. Furthermore the designers of both an FPGA and a Raw device must address the *grain size* issue—in other words, whether to implement a few powerful tiles or whether to use many small tiles, each with lower processing power.

This paper presents *SimpleFit*, an analytical framework that designers can use to reason about the division of resources in a VLSI chip. Although our analysis in this paper is focused on the Raw microprocessor, the analysis generalizes other chip multiprocessor architectures. Our objective in this paper is to gain more insight into cost-performance optimal designs given a fixed amount of resources.

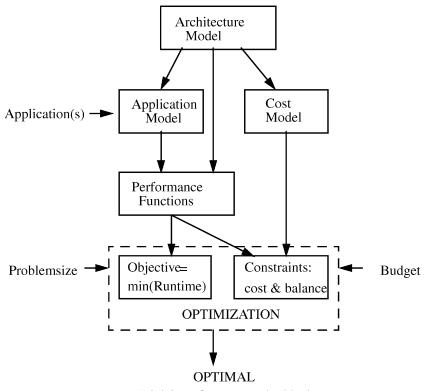

The framework presented in this paper focuses on the performance requirements of applications, introduces an *architecture model*, a *cost model*, and a *performance model* for applications, and defines an optimization process to search for performance optimal designs given a cost constraint.

The architecture model defines an architecture based on parameters that include the number of tiles P, the processing power of each tile p, the amount of memory in each tile m, the communication bandwidth out of each tile c, and a few other parameters, as shown in Section 2. The cost model estimates the cost in terms of chip area of realizing the given architecture with the specified set of parameters.

The performance model estimates the runtime of each application as a function of the problem size. Performance estimation is based on both 1) a characterization of the application and its algorithms in terms of its requirements, including processing steps, memory, and communication volumes and 2) the architecture model.

Together with a cost constraint defined in terms of the cost model, our performance model allows us to perform a constrained optimization on the independent architectural variables. We can, for example, compute the points or contours in the architectural space that correspond to the best performance for a given cost, lowest cost for a given level of performance, or best efficiency defined by performance/cost.

The algorithms used in this study have been adapted to the Raw system architecture illustrated in Fig. 1 by first partitioning them into subproblems that can fit within the Raw chip. Each subproblem is loaded from the external global RDRAM memory into the set of local memories in the tiles. Computation occurs on the subproblem and the results are stored back into external RDRAM. All the subproblems are visited (possibly multiple times) in sequence. The algorithmic slowdown due to blocking the problem in this manner is accurately modeled. Each subproblem is solved in parallel with a blocking algorithm. Applications studied in this paper include Jacobi Relaxation, Dense Matrix Multiply, Nbody, FFT, and Largest Common Subsequence.

The specific contributions of this paper include:

- a general framework for reasoning about the design space of VLSI-based parallel architectures, including models for cost and performance,

- insights on optimal grain size and balance in Raw microprocessors.

The remainder of this paper is organized as follows: Section 2 describes the three models developed in this paper: the performance model, the cost model, and the application model, and gives a qualitative analysis of cost and performance. Section 2.7 formulates the optimization process based on previous model assumptions. Section 3 gives our experimental results and Section 4 discusses related work. Section 5 concludes the paper.

## 2 FRAMEWORK

This section presents the analytical framework used in analyzing candidate designs in terms of their grain size and balance. We first start with a motivation for a study of grain size issues.

## 2.1 Motivation

Two key questions in the design of a Raw microprocessor involve the *grain size* of its tiles and their *balance*. The grain size reflects the sizes of various components inside the tiles such as memory, processing, and communication. A very coarse grain design would involve multiple issue superscalars for processing and large local memories. Very fine grain designs would be similar to contemporary FPGAs and include a few bits worth of logic and memory within each tile and a few wires connecting the individual tiles. Designs

Division of resources & chipsizes

Fig. 2. Analytical framework. The key components of the framework are the models and the optimization process. Given an application with an associated problem size and a fixed silicon area budget, the constraint equations are derived for the optimization. The nonlinear optimization process searches the machine configuration space that gives the minimal runtime for the application.

with a moderate grain size would involve very simple single-issue processors in each node.

Grain size and balance play a large part in determining the efficiency or performance per unit cost of a machine assuming a fixed total budget. If an engineer builds a small number of very large (coarse grain) nodes, a point of diminishing returns is reached where node performance increases very slowly (if at all) as node size is increased. On the other hand, building a large number of very small (fine grain) nodes will also result in diminishing returns as the communication costs dominate. The highest efficiency occurs at an optimal point between the two extremes. Similarly, as observed by Kung and Yeung et al. [18], [12], there is an optimal balance of resources between the processor, memory, and the communication components within a node.

While there has been much debate on this topic, few concrete results have been reported. Machine balance and grain size continues to be determined more by convenience and market forces than by engineering analysis. Our primary motivation in undertaking this study is to provide an analytical framework to enable engineers to obtain insights into the trade-offs in choosing various machine parameters.

Let us first provide an overview of the framework. Throughout the paper, execution times are measured in *machine cycles*, information in units of machine *words*, and cost in *SRAM bit equivalents (Sbe)*. As discussed in Section 2.4, an Sbe is the area occupied by one bit of SRAM memory.

#### 2.2 Overview of the Framework

Let us overview our analytical framework, illustrated in Fig. 2, by considering a simple machine model. In its simplest form, a parallel machine can be characterized by the number of tiles or nodes, P, the processing power of each node, p (operations per cycle), communication bandwidth of each node, c (words per cycle), and the amount of local memory per node, m (words).

For a given problem size and partitioning strategy, an application can be described by its processing, communication, and memory requirements per node or  $R_p$  (operations to be performed),  $R_c$  (words to be communicated), and  $R_m$  (words). The model used in the paper is not complex and is discussed in Section 2.3.

The performance of the application in terms of its runtime *T* is derived from the application requirements and the architectural model. If the processing time  $T_p = \frac{R_p}{p}$  and the communication time  $T_c = \frac{R_c}{c}$ , then, if processing and communication are fully overlapped, the runtime is given by  $T = max(T_p, T_c)$ .

We use cost models  $K_p(p)$ ,  $K_c(c)$ ,  $K_m(m)$  to map the machine parameters P, p, c, m into costs. In other words, the processor cost model  $K_p(p)$  provides the area cost of implementing a processor that can perform p operations per cycle. The total machine cost for a P processor machine is then  $K = P(K_p + K_c + K_m)$ .

Given an application with a fixed problem size N and an area budget B, a constrained optimization problem is defined with the objective of finding the optimal machine

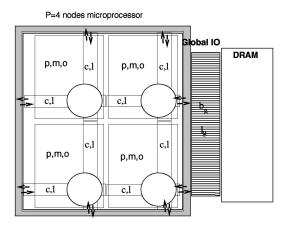

Fig. 3. A four node illustrative Raw system characterized by the parameters  $\langle P, p, m, c, l, o, b_g, l_g \rangle$ , where the processing power per node in operations per cycle is p, the amount of SRAM memory per node is m, the local communication bandwidth per node in words per cycle is c, the software overhead for a communication event in cycles is o, the single hop communication latency is I, the global off-chip communication bandwidth per Raw chip in words per cycle is  $b_g$ , and the RDRAM latency expressed in cycles is  $l_g$ .

configuration that gives the smallest runtime for that budget. In other words, the framework finds the set of architectural parameters P, p, c, m that yield a minimum value for *T* given that the cost *K* cannot exceed the available budget *B*. Or, more formally:

find P, p, c, mto minimize  $T = max(T_p, T_c)$ , subject to  $B \ge K$ .

As discussed in more detail later, the optimization process is sped up by a set of *balance constraints*. The balance constraints state that, for the optimal solution, the computation time and communication time must be equal and that the physical memory should fit the problem. The balance constraints greatly reduce the size of the search space and thus the complexity of the optimization procedure.

The following sections discuss each of the components of the framework and the optimization process in more detail.

## 2.3 Architecture Model

This section discusses parameters necessary for architecture characterization. Although several approaches to modeling the performance of a parallel computer have been proposed in the literature [2], [3], none are completely suited to modeling fine-grain parallel systems built on a chip. Fig. 3 shows our characterization of a Raw system using the parameters described below. Our machine characterization differs from previous ones in the sense that it captures both local and global communication performance and includes software overheads.

We choose as independent parameters the number of nodes, P, the processing power per node in operations per cycle, p, the memory per node m in words, the local communication bandwidth per node in words per cycle, c, the software overhead for communication in cycles, o, the single hop latency of the network, l, the global off-chip

communication bandwidth per chip in words per cycl,  $b_g$ , and the RDRAM latency expressed in cycles,  $l_q$ .

As an example, sending a local intertile message of length *L* words first involves spending *o* cycles in launching the message. The message header word travels, on average, a distance of  $k_d$  hops in the network using *l* cycles per hop. Because the bandwidth out of a node is *c* words per cycle, subsequent message words take  $\frac{1}{c}$  to enter the network. The receiving tile would also spend *o* cycles receiving the message. Thus, the communication time per message is:

$$T_c = 2o + k_d l + (L-1)\frac{1}{c}.$$

(1)

Writing a block of data to the off-chip RDRAM memory first involves an overhead o associated with starting up global communication. The latency of accessing the DRAM will be the sum of the latency of traversing the interconnection network in one dimension  $(k_d l/2)$  plus  $l_g$ , the DRAM latency. (We divide by two to indicate that RDRAM memory messages do not have to traverse both the X and Y network dimensions). The transfer rate of subsequent words will be the minimum of the local communication bandwidth and the global communication bandwidth per tile (since multiple tiles might be writing external memory). Thus the time for writing a block of size *L* to memory is:

$$T_g = o + \frac{k_d}{2}l + l_g + (L-1)max\left(\frac{1}{c}, \frac{P}{b_g}\right).$$

(2)

Communication locality can be captured at the application level by accounting for it in the average distance, that messages travel ( $k_d$ ). We ignore contention effects (e.g., resource and network contention) also because we assume that the compiler can statically orchestrate communication events much as in a virtual wires system. We also use a conservative approach in defining applications' communication requirements.

## 2.4 Cost Model

We use silicon area as a measure of cost. Silicon area reflects the fundamental cost of building a component and is a good basis for comparing alternatives as opposed to market price which includes many artificial factors. The cost model is based on CMOS microprocessors, SRAM and DRAM memories, and a mesh interconnection technology. For simplicity, we consider the off-chip RDRAM memory-free. Although our assumptions may change specific numerical results, the methodology for determining balance and grain size remains the same.

We normalize cost to units of SRAM bits, viz. one bit of SRAM takes one unit of area and, therefore, one unit of cost. We express the cost of all other components in terms of *SRAM bit equivalents* (Sbe).

We use the notion of relative density to enable the normalization of logic, memory, and communication areas into units of SRAM bit equivalents. Relative density captures the area impact of wires and more irregular structures, such as logic areas versus the more regular memory arrays. Although an SRAM bit comprises typically four to six transistors, we observe that the area it occupies is

TABLE 1 Relative Densities of Constituent VLSI Components

| Area                    | Relative density |

|-------------------------|------------------|

| CPU logic transistor    | 1 Sbe            |

| Router logic transistor | 1 Sbe            |

| SRAM bit                | 1 Sbe            |

| DRAM bit                | 1/16 Sbe         |

similar to the area of a logic transistor in a CPU die because of its regular structure and, therefore, its higher relative density. Thus, the chip size expressed in Sbe units is equivalent to the total number of transistors for logic areas (Table 1).

A DRAM bit is realized with one transistor and the area it occupies is 10-16 times smaller than an SRAM bit area. We arrived at this conclusion as the typical SRAM cell requires a wire grid of dimension  $3 \times 4$  compared to a DRAM cell implemented on the intersection of two wires. Factors such as the number of metal layers may change the relative density relations as more layers increase the density of logic areas. The logic area density is also reduced because of the greater amount of area devoted to wiring.

The following cost functions are based on empirical observations and statistics gathered on current implementations of superscalars and router chips:

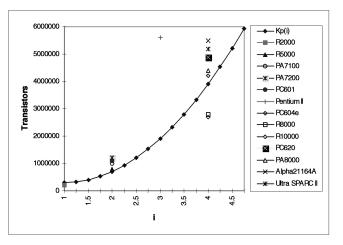

**Processor Cost**  $K_p$ . The processor cost model computes the area cost as a function of p. We find it convenient to relate p to cost  $K_p$  using an intermediate parameter i, which is the number of issue units i in the processor. Thus, i = 4implies a 4-way superscalar with a maximum of four operations per cycle.

We model the relationship between processing cost and instruction issue structure as a quadratic curve, which captures the cost increase due to multiple issue superscalars:

$$K_p(i) = B_p + K_{ps}(i-1)^2.$$

(3)

In the above, a cost of  $B_p$  is required to achieve a single issue processor with i = 1.

We relate processing power *p* and the number of issue units *i* using:

1

$$\rho = \sqrt{i},\tag{4}$$

This model captures the relationship between performance and cost due to more aggressive clock rates of lower issue processors. Typically, single issue designs obtain 1.6 to 2 times faster clock rates than corresponding high-issue rate processors. It also captures the fact that it is easier to obtain performance close to the theoretical maximum cycles per instruction in lower-issue processors as they require a smaller amount of instruction-level parallelism in applications.

Studying the layout of some simple RISC processors [13], [21], [20], [15] leads to a base cost of  $B_p = 2.5 \times 10^5$  transistor. That is, a minimal single issue 64-bit processor can be built in the area of 250K SRAM bits or with 250K logic transistors. A cost constant of  $K_{ps} = 4 \times 10^5$  Sbe was arrived at from the study of some high-end processors [29], [27], [28], [15].

Fig. 4. Comparison between the processor cost function  $K_p(i)$  and cost of logic areas in current superscalar microprocessors. Cache memory areas are factored out.

For validation, Fig. 4 compares the number of transistors dedicated to logic in several superscalar microprocessors with our cost model for  $K_p(i)$ . We observe that, for higherissue superscalars, the variation in the number of transistors dedicated to logic areas is large. This variation is caused by important differences in implementation of components like issue structure, scheduling, and memory interfaces. A more detailed cost model for superscalars may also deal with the cost impact of dynamic or static issue structures, scheduling, and memory interfacing.

**Memory Cost.** We approximate memory cost as a linear function of capacity *m*:

$$K_m(m) = B_m + Wm. (5)$$

Here, *m* is the memory size in words,  $K_{ms}$  is the cost per word of memory, and  $B_m$  is the fixed overhead cost of the memory. This overhead includes logic for translation, address decode, data multiplexing, and memory peripheral circuitry. For our calculations, we assume that W(wordsize) = 64 and the overhead,  $B_m$ , is  $5 \times 10^4$ .

**Communication Cost.** The main components of a typical router comprise a routing module, a crossbar arbiter, and input output modules, often including large FIFOs. We observe that most of the area in current router chips is taken up by FIFOs and pad frames (circa 20 percent). Crossbar logic usually occupies a small part of the total area.

The amount of FIFOs depends on such factors as the number of virtual channels. The area of queues reflects the size of message flits and a length which is typically 16-20 flits. A flit is the number of bits transferred in one cycle and, therefore, it also equals c expressed in bits. One word per cycle communication bandwidth thus requires a flit size of one word. Although not necessary, we also assume the flitsize is equal to the physical channel width. We denote the dimension of the network as n. The total number of bidirectional channels is then 2n. Our results focus on two-dimensional networks, so n = 2 for most of this paper. We have found that the area of routers is proportional with the number of queue sets used in implementing virtual channels, the flit size, the dimension

| Router    | Transistors | Estimated                    | Type              | Network | Flits | $F_l$ | Q | Pins    |

|-----------|-------------|------------------------------|-------------------|---------|-------|-------|---|---------|

| J machine | 29000       | 29050                        | wormhole          | 3D mesh | 9     | 3     | 1 | -       |

| Postech   | 30140       | 31400 virtual cut-through 21 |                   | 2D mesh | 8     | 8     | 1 | 100     |

| Mosaic C  | 60000       | 44200                        | wormhole, asynch. | 2D mesh | 8     | 4     | 3 | c.a. 88 |

| Chaos     | 110000      | 121000                       | chaotic           | 2D mesh | 16    | 20    | 3 | 132     |

| RDT       | 320000      | 111400                       | wormhole, 2v      | 3D RDT  | 18    | 16    | 2 | 299     |

| RR        | 600000      | 625000                       | adaptive, 5v      | 2D mesh | 75    | 16    | 5 | 300     |

In the Type column, we give the number of virtual channels where necessary, e.g., 2v means two virtual channels. The second and third columns compare the actual number and the estimated number of transistors. With Flits, we show the flit size or the number of bits transferred in one cycle.  $F_l$  shows the length of FIFOs in flits and Q shows the set of queues in the design often reflecting the number of virtual channels.

of the network, and the length of the FIFOs. The cost function for the routers is described in the following equation:

$$K_c(c) = B_c + K_{cs}W \times F_l \times 2n \times Q \times c.$$

(6)

In the equation above,  $F_l$  is the length of the FIFOs and Q is the number of queue sets due to virtual channels. Our results use Q = 1. The communication cost factor,  $K_{cs}$ , is derived by fitting the cost function equation with the areas of routing chips shown in Table 2.

For our calculations, we use  $K_{cs} = 25$ . For example, a router with a 64 bit flit size and with one set of queues, each with length 16 flits, takes approximately a 125,000 logic transistor area in our model.

The base area for a router,  $B_c$ , is estimated at  $2.5 \times 10^4$ . We arrive at this from a study of simple routers [17], [16], [13], [22]. Examples of routers with the number of transistors used in current implementations are shown in Table 2. The estimates using our communication cost model are also shown. The comparison indicates that our cost model reflects relatively accurately the area occupied by these routers except the RDT [14] router chip that has more than half of its area devoted to a multicast mechanism module and a bit-map generator.

**Global Communication Cost.** We approximate global communication cost as a linear function of global off-chip communication capacity. The base area for global I/O,  $B_{bg} = 10^4$ , is estimated to be somewhat smaller than a simple router area as no routing functions are necessary. The global communication bandwidth is limited by the maximum number of pins a packaging technology will allow. As current microprocessor packaging technologies use from 100 to several hundred pins, we assume that, in 10-12 years, packaging will allow no more than roughly 2,000 pins. The maximum possible global bandwidth is then  $b_{max} = 2,000/W$ . The global communication cost factor,  $K_{bs} = 10^5$ , multiplied with the wordsize is approximately the cost in SRAM bit equivalents of one word per cycle of global I/O bandwidth:

$$K_{bg}(b_g) = \begin{cases} \infty & \text{if } b_g > b_{max} \\ B_{bg} + K_{bsg} W b_g & \text{otherwise.} \end{cases}$$

(7)

**Global Latency Cost.** For simplicity, we assume this cost as a constant reflecting the more or less constant speed of DRAM access over time.  $B_{lq}$  is estimated at  $10^5$ :

$$K_{lg}(l_g) = B_{lg}.$$

(8)

**Total Cost of the System.** The total cost of the system is equal to the sum of its components:

$$K(x) = P(K_p(p) + K_c(c) + K_m(m)) + K_{bg}(b_g) + K_{lg}(l_g).$$

(9)

#### 2.5 Application Model

The application model contains functions and parameters that are necessary for application performance characterization. To predict the performance of an application with a particular machine configuration, we assume that the resource demands are uniform over time and that processing, local, and global communication can be completely overlapped. Some algorithms, such as those used in dynamic programming, also require the estimation of the algorithmic imbalance or the idle time due to synchronization overhead. Applications with several phases can be handled by dividing the application into its phases and characterizing each phase separately. Our assumption that processing, local, and global communication are overlapped imposes constraints on how the problem is partitioned and on the total amount of memory required. As we will show later, besides the memory needed to hold the problem, local and global communication buffers are required in order to be able to overlap communication times.

Our application model does not distinguish between different forms of parallelism and types of functional units, i.e., we assume that the parallelism available in the application can be utilized equally well in a multiple issue or in a multitle design.

We will exemplify the concepts of this section by analyzing the Jacobi relaxation problem. The requirements of the other applications considered in this paper are presented in Table 6. The Jacobi Relaxation problem is an iterative algorithm which, given a set of boundary conditions, finds discretized solutions to differential equations of the form  $\nabla^2 A + B = 0$ . Each step of the algorithm replaces the value at each node of a grid with the average of the values of its nearest neighbors.

The original Jacobi problem defined by a grid of size N is partitioned in subgrids of size N', as illustrated in Fig. 5. Each subgrid or subproblem is solved by storing the subproblem of size N' in the internal memory of a Raw microprocessor and running a blocking relaxation algorithm. After a given number of phases, the subgrid is stored in external RDRAM and the next subgrid is loaded. Clearly, a given subgrid has to be loaded and operated upon multiple times to reflect the effect of synchronization with the values computed in neighboring subgrids.

Because values from neighboring subgrids do not impact the relaxations on a given subgrid stored in the micro-

Fig. 5. Jacobi Relaxation. The problem of size N is first partitioned in subproblems of size N'. Each subproblem is solved with blocking on P processors. Each processor receives bordering data from its four neighbors and sends its data along borders to its neighbors. Subproblems are resynchronized after a number of iterations.

processor, the number of iterations needed for convergence increases. We choose  $i_s = \sqrt{N'}/2$  as the number of iterations after which resynchronizations must occur between subproblems. Starting with some boundary conditions, this means propagating border values to all points in a subproblem. We chose the total number of iterations as being  $i_t = N^2$ , giving an error reduction factor of 10.

Let us analyze the requirements of this application.

**Required Processing per Node**  $R_p$ . This requirement reflects the total amount of computation required per Jacobi node given the algorithmic assumptions described above. The total number of operations for each point is three additions and one multiplication:

$$R_p = i_t 4 \frac{N}{P} = 4 \frac{N^3}{P}. \qquad P \in [1, N].$$

(10)

**Required Amount of Memory Words per Node**  $R_m$ . The required memory is comprised of the memory required to solve the subblock of size N' and also the memory buffers needed to overlap local and global communication:

$$R_m = \frac{N'}{P} + 4\sqrt{\frac{N'}{P}} + 2\frac{N'}{P} = 3\frac{N'}{P} + 4\sqrt{\frac{N'}{P}}.$$

(11)

Required Number of Words of Local Communication per Node  $R_c$ . The required local communications is the total amount of data sent or received during the whole execution time. For any iteration, each processor requires the bordering points from its neighbor processors:

$$R_c = i_t \times 8\sqrt{\frac{N'}{P}} \times \frac{N}{N'} = 8\frac{N^3}{\sqrt{N'P}}.$$

(12)

**Required Local Communication Events**  $R_o$ . These events incur a software penalty for initiating a communication step. It reflects the total number of times a local send or receive is issued:

$$R_o = R_c \times \frac{1}{\sqrt{\frac{N'}{P}}}.$$

(13)

**Required Latency of Events**  $R_l$ . Reflects the total number of times a local send is issued:

$$R_l = R_c \times \frac{1}{2\sqrt{\frac{N'}{P}}}.$$

(14)

**Required Global Communication**  $R_{bg}$ . Reflects the total amount of words of global communication per chip:

$$R_{bg} = \frac{i_t}{i_s} 2N = 4 \frac{N^3}{\sqrt{N'}}.$$

(15)

**Required Global Communication Events**  $R_{lg}$ . Reflects the total times global sends or reads are initiated per chip:

$$R_{lg} = \frac{R_{bg}}{N'}.$$

(16)

# 2.6 Performance Functions

The performance functions estimate the running time of an application in terms of application requirements and architecture parameters.

**Runtimes**  $\langle T, T_p, T_c, T_g \rangle$ . Let the times for processing, local communication, and global communication be  $T_p, T_c$ , and  $T_g$ , respectively. Under the assumptions that local and global communication time are overlapped with computation, the parallel runtime is defined as the maximum of these times:

$$T = max(T_p, T_c, T_g),$$

$$T_p = \frac{R_p}{p} + R_o o + R_{lg} o,$$

$$T_c = \frac{R_c}{c} + R_l k_d l,$$

$$T_g = \frac{R_{bg}}{b_g} + R_{lg} \frac{k_d}{2} l + R_{lg} l_g.$$

(17)

As an example, if the number of operations that must be performed is  $R_p$  and the processing power is p operations per cycle, then the processing time is simply  $R_p/p$ . Similarly, if the number of events incurring the message overhead (o cycles) is  $R_o$ , then the time wasted in message overhead activity is  $R_o o$ .

#### 2.7 The Optimization Problem

In this section, we describe in more detail the optimization procedure. The problem solved is the following *constrained based nonlinear optimization problem:*

**Given:** A fixed chip area or budget *B* and a problem size *N*. **Objective:**

$$min(T(N, N', x)) \tag{18}$$

is subject to the constraints given below, where *x* is a specific machine configuration  $\langle p, P, m, c, o, l, b_g, l_g \rangle$ . The solution of this optimization is the optimal machine configuration:  $x_{opt} = \langle p, P, m, c, o, l, b_g, l_g \rangle_{opt}$  and the optimal subproblem size:  $N'_{opt}$ .

## Constraints.

1. Budget *B* must be greater than or equal to the total cost. The total cost of the system is computed as the sum of its components:

$$B \ge P(K_p + K_c + K_m) + K_{bg} + K_{lg}.$$

(19)

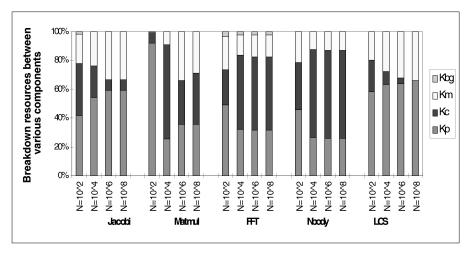

Fig. 6. Breakdown of chip areas for processing, memory, local communication and global communication that give optimal machine configurations for a budget of one billion logic transistor equivalent area.

It is expedient to use an additional set of balance constraints, as given below, when the communication and computation are overlapped. The balance constraints focus the search for the optimal solution to balanced machine configurations. In other words, the second and third equations state that communication and computation times should be equal. If they are not equal, we can take resources from the faster component and give them to the slower component to improve runtime. The last balance constraint states that the memory should fit the problem. If the memory is larger than this amount, it can be reduced without impacting performance. When local and global communication times are equal and memory fits the problem, the machine configuration is balanced for the application. In a balanced machine, each resource is utilized to its fullest. The balance constraints greatly reduce the search space and, thus, the complexity of the optimization procedure.

2. Balanced local communication with computation:

$$T_p = T_c. (20)$$

3. Balanced global communication and computation:

$$T_g = T_p. \tag{21}$$

4. Memory on a processor element must fit the memory required for a block. Besides the memory required for actual computations,  $R_m^a$ , buffers for local and global communications,  $R_m^l, R_m^b$ , are allocated because of overlapping conditions:

$$m = R_m = R_m^a + R_m^l + R_m^g.$$

(22)

# **3** ANALYSIS

In this section, we study a set of applications in the context of the framework presented. The applications are: Jacobi Relaxation, Dense Matrix Multiply, Nbody, FFT, Largest Common Subsequence. We chose these applications becouse they are diverse and require conflicting machine performances to run efficiently. The optimization procedure has been implemented in Mathematica. We use a three cycle software overhead, a 100 cycle DRAM access latency, and assume an MIPS R2000 ISA for instruction latencies. We also counted an 8 Kbyte SRAM-based instruction and data cache per node.

In all the experiments, we used a budget of one billion SRAM bit equivalents or the area required for one billion logic transistors. This budget is achievable in 10-12 years as projected by the Semiconductor Industry Association (SIA) given a 10-20 percent growth rate per year of die areas and a growth rate in transistor counts of between 60 and 80 percent per year due to increasing densities.

# 3.1 Application Specific Results

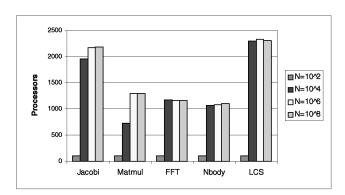

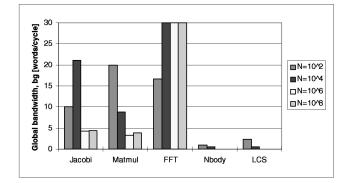

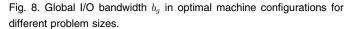

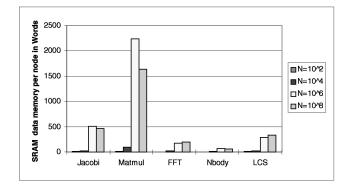

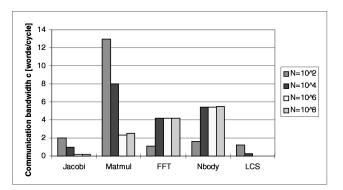

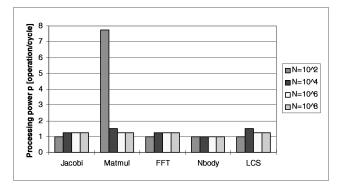

Fig. 6 shows the optimal division of chip resources for the various applications as a function of problem size. The optimal amount of each resource is shown in greater detail in Fig. 7, Fig. 8, Fig. 9, Fig. 10, and Fig. 11.

Perhaps the most important result from Fig. 6 is that the amount of area devoted to processing and local communication is more or less constant at about 75 percent for all the applications and problem sizes. There is a variance,

Fig. 7. Number of processors in optimal machine configurations for different problem sizes.

however, across the programs in terms of how much of this area should be devoted to computation versus communication. These two components could be traded, for example, at runtime in true FPGA systems. Although the 25 percent area dedicated to memory is less than what we have in today's microprocessors, it is still a significant portion of the chip. Future applications, such as media and streaming applications will likely require even less memory because fast local and global communication can eliminate the need for buffering an intermediate state.

The global communication bandwidth of 30 words per cycle is the maximum achievable given a packaging technology allowing 2,000 pins. The only application that is I/O limited and requires this bandwidth is FFT. All the other applications have a negligible area allocated to global communication. The total chip area for global communication is relatively small, even for FFT. Therefore, providing the maximum possible global bandwidth is not a bad idea in a final configuration.

As we can see, the relative communication area required is small in applications such as Jacobi and LCS as they also show good spatial locality. These applications can use most of the resources for processing. FFT and Nbody require the largest communication area with an optimal communication bandwidth between four and five words per cycle. The division between processing and memory areas is uniform.

The matrix multiplication based on Connor's memory efficient blocking algorithm gives the most uniformly divided configuration. For this application, memory, local

Fig. 9. Local SRAM data memory m per node in optimal machine configurations.

Fig. 10. Local communication bandwidth *c* in optimal machine configurations for different problem sizes.

communication, and processing areas are approximately equal.

The amount of memory per node obtained is relatively small compared to modern day multiprocessors in all applications. The reason is twofold. First, the total amount of memory in the entire Raw chip is still quite large since it is the product of P and m. Second, fast local communication obviates the need for huge amounts of local memory. The matrix multiplication required the largest amount of memory giving a total of 24 Kbytes per node. The smallest memory is required for Nbody.

For all the applications, the optimal processing power obtained is equivalent to a single-issue processor. The total number of processors P varied between 1,100 to 2,310 for large problem sizes.

Although the optimal machine configurations obtained vary for different applications, problem sizes, and budgets, the general trends for various applications are similar. Accordingly, for the applications studied, assuming a one billion logic transistor equivalent area, we recommend building a Raw chip with approximately 1,000 tiles, 30 words/cycle global I/O, 20 Kbytes of local memory per node, three to four words/cycle local communication bandwidth, and single-issue processors. This configuration will give performance near the global optimum for applications studied.

## 3.2 Sensitivity of Grain Size

The framework helps answer many other questions about machine configurations. Let us study the *sensitivity* of

Fig. 11. Processing power p in optimal machine configurations for different problem sizes.

TABLE 3 Solutions that Come within 25 Percent of the Optimal for a Problem Size of  $10^8$  with the Smallest Number of Nodes P

| Problem | P    | N'      | С    | p    | m     | $b_g$ | $PK_p$ | $PK_c$ | $PK_m$ | $K_{bg}$ | $K_{lg}$ |

|---------|------|---------|------|------|-------|-------|--------|--------|--------|----------|----------|

| Matmul  | 1290 | 548x548 | 2.6  | 1.25 | 1640  | 3.9   | 35     | 35     | 28     | 0.01     | 0.01     |

| (18%)   | 826  | 685x685 | 1.7  | 2    | 3975  | 2.5   | 46     | 20     | 32     | 0.01     | 0.01     |

| Jacobi  | 2180 | 302230  | 0.19 | 1.25 | 464   | 4.4   | 60     | 7.4    | 32.6   | 0.01     | 0.01     |

| (24%)   | 811  | 302230  | 0.3  | 2    | 538   | 5     | 77     | 5.5    | 16     | 0.01     | 0.01     |

| Nbody   | 1100 | 8306    | 5    | 1    | 61    | 0.06  | 26     | 60     | 13     | 0.0002   | 0.01     |

| (21%)   | 799  | 295145  | 5    | 1.5  | 2954  | 0.001 | 28     | 47     | 24     | 0.00001  | 0.01     |

| FFT     | 1160 | 68718   | 4.2  | 1.25 | 178   | 30    | 31     | 50     | 15     | 0.2      | 0.01     |

| (23%)   | 356  | 3518440 | 2.7  | 1.75 | 29594 | 30    | 17     | 10     | 71     | 0.2      | 0.01     |

| LCS     | 2310 | 193427  | 0.01 | 1.25 | 337   | 0.015 | 63     | 3.7    | 32     | 0.0001   | 0.01     |

| (23%)   | 1119 | 4354    | 0.05 | 1.75 | 499   | 0.015 | 73     | 2.4    | 23     | 0.0001   | 0.01     |

The first row of each application shows the global optimum and the second row shows the solution with the minimum number of processors and performance within 25 percent of the optimal. The numbers in parentheses show the performance degradation compared to the global optimum for the configurations with the minimum processors. The first columns between P to  $b_g$  represent the optimal machine configuration and the columns from  $PK_p$  to  $K_{lg}$  are the chip sizes in percent of the total cost.

performance to the machine configuration near the optimum machine configuration point. This study is useful to determine a machine configuration that is robust across many applications. As an example, let us determine the machine configuration with the smallest number of nodes whose performance is within 25 percent of the optimal configuration.

Results are shown in Table 3. For each application, the first row gives the optimal configuration. The second row gives the configuration with the smallest number of nodes under the condition that the performance is no worse than 25 percent of the optimal. As we can see, balanced machine configurations with fewer nodes usually take advantage of the parallelism available in superscalar processors. However, for all the applications studied, the configuration that gave best performance used nodes based on 2-way superscalars at most.

# 3.3 Sensitivity to Different Processor Cost Model Assumptions

In the analysis presented in this section, we used a quadratic cost model for the processors. In the following,

we analyze the sensitivity of optimal machine configurations to a slightly different processor cost model.

Table 4 compares machine configurations obtained with two processor cost models. For each application and each parameter, two experimental values are shown. The first value corresponds to the case when the quadratic processor model is used; the values in the parentheses correspond to a processor cost function  $K_p(i) = B_p + K_{ps}(i-1)^{3/2}$  or assume a less dramatic impact on chip area with multiple issue designs. As we can notice from Table 4, the variations in the optimal balanced machine configurations are very small. The framework suggests simple processors even in the case of the less expensive processor model. The explanation is that the applications used in this study are highly parallel, the cost of local communication is very low in applications with good locality, and adding more functional units is still expensive (the processor cost function is nonlinear). Additionally, the impact of communication latency is further reduced if it is overlapped with computation.

| Problem | Size            | P          | с          | p           | m          | $b_g$        |

|---------|-----------------|------------|------------|-------------|------------|--------------|

| Matmul  | 10 <sup>8</sup> | 1290(1253) | 2.6(2.5)   | 1.25 (1.25) | 1640(1680) | 3.9(3.8)     |

| Matmul  | $10^{6}$        | 1290(1250) | 2.3(2.1)   | 1.25(1.25)  | 2230(2295) | 3.3(3.2)     |

| Matmul  | $10^{4}$        | 724(657)   | 8 (8.69)   | 1.5(1.75)   | 97(107)    | 8.8(13)      |

| Jacobi  | $10^{8}$        | 2180(2320) | 0.19(0.17) | 1.25(1)     | 464(437)   | 4.4(4.2)     |

| Jacobi  | $10^{6}$        | 2171(2310) | 0.19(0.17) | 1.25(1)     | 502(473)   | 4.2(4)       |

| Jacobi  | $10^{4}$        | 1950(1850) | 1 (0.96)   | 1.25(1.25)  | 25(26)     | 21(21)       |

| Nbody   | $10^{8}$        | 1100(1103) | 5(5.5)     | 1(1)        | 61(61)     | 0.06(0.06)   |

| Nbody   | $10^{6}$        | 1080(1080) | 5(5.4)     | 1(1)        | 67(67)     | 0.06(0.06)   |

| Nbody   | $10^{4}$        | 1070(1070) | 5(5.4)     | 1(1)        | 8(8)       | 0.5(0.5)     |

| FFT     | $10^{8}$        | 1160(1130) | 4.2(4.1)   | 1.25(1.25)  | 178(211)   | 30(30)       |

| FFT     | $10^{6}$        | 1160(1132) | 4.2(4.1)   | 1.25(1.25)  | 178(183)   | 30(30)       |

| FFT     | $10^{4}$        | 1160(1143) | 4.2(4.1)   | 1.25(1.25)  | 178(27)    | 30(30)       |

| LCS     | $10^{8}$        | 2310(2460) | 0.01(0.01) | 1.25(1)     | 337(317)   | 0.015(0.014) |

| LCS     | $10^{6}$        | 2330(2475) | 0.01(0.01) | 1.25(1)     | 291(274)   | 0.014(0.014) |

| LCS     | $10^{4}$        | 2290(2436) | 0.25(0.2)  | 1.5(1)      | 20(19)     | 0.25(0.4)    |

TABLE 4 Sensitivity of Optimal Machine Configuration to Processor Cost Model Assumptions

Breakdown of optimal machine configurations for three problem sizes and two processor cost models. The first model corresponds to a quadratic curve between processor costs and issue rate  $K_p(i) = B_p + K_{ps}(i-1)^2$ . The numbers in the parentheses are for a processor cost function  $K_p(i) = B_p + K_{ps}(i-1)^{3/2}$  assuming a less dramatic impact on chip area with multiple issue designs. Columns P to  $b_g$  represent the optimal machine configuration.

| Problem | Size            | P          | с          | p           | m          | $b_g$        |

|---------|-----------------|------------|------------|-------------|------------|--------------|

| Matmul  | $10^{8}$        | 1290(1286) | 2.6(2.6)   | 1.25 (1.25) | 1640(1635) | 3.9(3.9)     |

| Matmul  | $10^{6}$        | 1290(1286) | 2.3(2.2)   | 1.25(1.25)  | 2230(2230) | 3.3(3.3)     |

| Matmul  | $10^{4}$        | 724(716)   | 8 (9.4)    | 1.5(1.75)   | 97(98)     | 8.8(14.2)    |

| Jacobi  | $10^{8}$        | 2180(2179) | 0.19(0.18) | 1.25(1.25)  | 464(458)   | 4.4(4.4)     |

| Jacobi  | $10^{6}$        | 2171(2191) | 0.19(0.22) | 1.25(1.25)  | 502(403)   | 4.2(4.7)     |

| Jacobi  | $10^{4}$        | 1950(1955) | 1 (0.98)   | 1.25(1.25)  | 25(25)     | 21(21.8)     |

| Nbody   | 10 <sup>8</sup> | 1100(1032) | 5(5.9)     | 1(1.25)     | 61(59)     | 0.06(0.5)    |

| Nbody   | $10^{6}$        | 1080(1013) | 5(5.9)     | 1(1.25)     | 67(58)     | 0.06(0.5)    |

| Nbody   | $10^{4}$        | 1070(1000) | 5(5.8)     | 1(1.25)     | 8(9)       | 0.5(0.5)     |

| FFT     | 10 <sup>8</sup> | 1160(1245) | 4.2(3.9)   | 1.25(1)     | 178(153)   | 30(30)       |

| FFT     | $10^{6}$        | 1160(1244) | 4.2(3.9)   | 1.25(1)     | 178(166)   | 30(30)       |

| FFT     | $10^{4}$        | 1160(1255) | 4.2(3.9)   | 1.25(1)     | 178(20)    | 30(30)       |

| LCS     | $10^{8}$        | 2310(2332) | 0.01(0.01) | 1.25(1.25)  | 337(268)   | 0.015(0.014) |

| LCS     | $10^{6}$        | 2330(2343) | 0.01(0.01) | 1 25(1 25)  | 291(232)   | 0.014(0.014) |

TABLE 5 Sensitivity of Optimal Resource Partitioning to Communication Overlapping Assumptions

Breakdown of optimal machine configurations for three problem sizes and two overlapping models. The first overlapping model corresponds to the case when all communication latencies can be overlapped with computations. The numbers in the parentheses correspond to the case when only half of the communication time can be overlapped with computation. Columns P to  $b_g$  represent the optimal machine configuration.

1.5(1.25)

0.25(0.2)

# 3.4 Sensitivity to Communication Overlapping Asssumptions

$\overline{10^4}$

2290(2289)

LCS

In the analysis presented in this section, we assumed that communication time can be completely overlapped with computation. We used this assumption because it has significantly reduced the complexity of the optimization problem and it is a reasonable assumption for many regular applications (especially if they are statically scheduled). However, it is possible to extend the model with an extra parameter, the *overlapping factor*, to account for the situation when complete overlapping is not possible. We define the overlapping factor as the ratio between the overlapped and total communication times. As an example, to study the sensitivity of optimal resource partitioning to the overlapping factor, we determined the machine configuration assuming that only half of the communication time can be overlapped with computation.

Results for two machine configurations are shown in Table 5. For each application and each parameter, two experimental values are given. The first value corresponds to the completely overlapped case, the values in the parentheses correspond to an overlapping factor equal to 0.5. As we can notice, the variations in the optimal balanced machine configurations are very small. The explanation is that none of the applications are memory bound, meaning that the extra memory required for local and global communication buffering in the overlapped case is not very significant. Similarly, the added communication times

are overlapped is not significantly impacting the execution time and thus the optimal partitioning of resources.

0.25(0.51)

# 3.5 Design Comparisons

20(20)

The framework also allows us to compare competing designs for the same budget. As an example, let us compare the two designs: 1) using on-chip SRAM and routers with 16-flit FIFOs and 2) using only a small SRAM cache and the rest of the memory in on-chip DRAM as well as small 2-flit FIFOs. We derive the performance/cost optimal configurations and look to application performance for different problem sizes.

Since DRAM densities are much higher than SRAM densities we can have more memory per node in alternative (2). One problem in using DRAMs is that the access latency is higher than corresponding SRAMs. To reduce the impact of the latency, we include a small SRAM cache in each node and assume that the SRAM cache results in a near perfect hit rate (this assumption can be made because the total amount of SRAM per Raw chip is very large even for a small SRAM per Raw tile). Case 2 also has small FIFOs—with good static scheduling of the communication channels, the need for deep FIFO's is reduced.

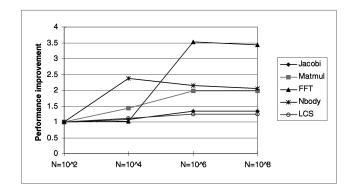

The question is: How much do these changes impact the performance of applications given performance/cost optimal partitioning of resources in both cases? Fig. 12 shows the performance ratio between the second and the first designs. It is easy to see that the larger amount of on-chip memory in Case 2 results in significantly higher

TABLE 6 Overview Application Requirements

| Application | $R_p$                 | $R_c$                     | $R_l$                       | $R_o$                       | $R_m$                                  | $R_{bg}$                 | $R_{lg}$                   |

|-------------|-----------------------|---------------------------|-----------------------------|-----------------------------|----------------------------------------|--------------------------|----------------------------|

| Jacobi      | $4\frac{N^3}{P}$      | $8\frac{N^3}{\sqrt{N'P}}$ | $4\frac{N^3}{N'}$           | $8\frac{N^3}{N'}$           | $3\frac{N'}{P} + 4\sqrt{\frac{N'}{P}}$ | $4\frac{N^3}{\sqrt{N'}}$ | $4\frac{N^3}{\sqrt{N'N'}}$ |

| Matmul      | $2\frac{N^3}{P}$      | $4\frac{N^3}{N'\sqrt{P}}$ | $2\frac{N^3\sqrt{P}}{N'^3}$ | $4\frac{N^3\sqrt{P}}{N'^3}$ | $7\frac{N'2}{P}$                       | $2\frac{N^3}{N'} + N^2$  | $2 \frac{N^3}{N'^3}$       |

| Nbody       | $2\frac{N^2}{P}$      | $2\frac{N^2}{P}$          | $\frac{N^2}{P}$             | $2\frac{N^2}{P}$            | $\frac{N'}{P}$                         | $4\frac{N^2}{N'}$        | $\frac{N^2}{N^{\prime 2}}$ |

| FFT         | $12\frac{N}{P}\log N$ | $2\frac{N}{P}\log N$      | $\frac{N}{N'} \log N$       | $2\frac{N}{N'}\log N$       | $4\frac{N'}{P}$                        | $2N\log N$               | $2\frac{N}{N'}\log N$      |

| LCS         | $2\frac{N^2}{P}$      | $2\frac{N^2}{N'}$         | $\frac{N^2}{N'}$            | $2\frac{N^2}{N'}$           | $4\frac{N'}{P}$                        | 4N                       | $\frac{N}{N'}$             |

Fig. 12. Performance comparison between two cost optimal designs each with a budget of one billion logic transistor area. In the first design, we use SRAM and routers with 16 flit FIFOs, while in the second design we use on-chip DRAM with a 1 Kbyte SRAM cache per node and 2-flit FIFOs.

performance. Assuming a fairly large 10 percent local miss rate (between the local SRAM and local DRAM), an on-chip DRAM latency of 10 cycles, one cycle SRAM latency, 25 percent memory instructions, the performance improvement in Case 2 is reduced by 25 percent to a speedup of 1.12 to 2.62 for the applications studied.

# 4 RELATED WORK

There are several research efforts that have defined a set of analytical models that allow estimation of system performance metrics. In this section, we briefly mention a few of these research works.

One of the first works incorporating technology, architecture, and packaging models in a framework is SUSPENS [7]. SUSPENS is a generic systems-level approach, covering the circuit and systems level of abstraction. The GENESYS framework [5] assimilates the entire hierarchical description of a microprocessor chip through a concise set of input parameters and projects its key performance metrics by engaging a set of interrelated models, incorporating both physical and empirical knowledge. SimpleFit is a much higher level framework than GENESYS and it has no physical models incorporated. In contrast, SimpleFit incorporates an analytical model for application runtime behavior, enabling optimization of architectures for different applications.

The LogP model [2] is a simple parallel machine model intended to serve as a basis for developing portable parallel algorithms. Alexandrov et al. defined the LogGP [11] model as an extension of LogP to capture the large bandwidth requirements of applications using long message primitives. LoGPC [9] leverages the performance parameters of LogP and LogGP and extends the analysis with a more detailed model of the DMA pipeline and a network contention component. The LoPC model [8] extended the LogP model with a resource contention model. The performance model in SimpleFit is using a similar set of parameters for modeling the most important performance aspects of a tiled single chip system.

There has also been a lot of interest in analytical models for caching. Some of the earliest work in cache area modeling has been done by Mulder et al. [6]. The area for a simple single-ported SRAM cell has been empirically found to be 0.6 register bit equivalents (RBE). This is comparable to the empirical estimation done in SimpleFit where an SRAM bit area is assumed to be equivalent with a CPU logic bit.

Another direction where analytical modeling is used is for estimating and optimizing microprocessor power dissipation at the architectural level. Wattch [10], for example, is a recent architectural simulator that estimates CPU power consumption by using parameterizable power models.

SimpleFit leverages some aspects of the early work on grain size for multiprocessor systems by Yeung et al. [12]. It goes, however, to a greater level of detail and focuses on single-chip tiled architectures as opposed to multiprocessor systems.

## 5 CONCLUSIONS

This paper describes SimpleFit, a novel framework for reasoning about single chip tiled microprocessors, such as Raw, with replicated, fine-grain processing elements. The framework uses a machine characterization that considers processing, memory, local and global communication, and latency as separate machine resources. This is a unique characterization of machine space since it captures the effects of locality by treating local and global communication separately. The framework incorporates a cost model based on empirical observations and statistics gathered on current implementations of superscalars and router chips.

The framework recognizes the importance of balance in good design and integrates this idea with a cost and performance model to provide a useful design tool. Having provided this framework, this paper chooses a diverse application suite in order to exercise the framework and to address some general questions in parallel computer design in general. More specifically, it addresses the questions of on-chip resource division in the MIT Raw microprocessor.

Although the optimal machine configurations vary for different applications, problem sizes, and budgets, the general trends are consistent. The framework further suggested that, for the applications studied and assuming a one billion logic transistor equivalent area, designers should build a system with about 1,000 nodes, 30 words/ cycle of global I/O, 20 Kbytes of local memory per node, three to four words/cycle local communication bandwidth, and single-issue processors for optimal performance.

## ACKNOWLEDGMENTS

The research is funded by US Defense Advanced Research Projects Agency contract #DABT63-96-C-0036. The authors are grateful to Tom Knight, Jonathan Babb, and Matt Frank for many relevant discussions on cost modeling, and the anonymous reviewers for their very valuable comments and help with earlier drafts of the paper.

## REFERENCES

- [1] E. Waingold, M. Taylor, D. Srikrishna, V. Sarkar, W. Lee, V. Lee, J. Kim, M. Frank, P. Finch, R. Barua, J. Babb, S. Amarasinghe, and A. Agarwal, "Baring It All to Software: Raw Machines," Computer, pp. 86-93, Sept. 1997.

- [2] D. Culler, R. Karp, D. Patterson, A. Sahay, K. Schauser, E. Santos, R. Subramonian, and T. Eicken, "LogP: Towards a Realistic Model of Parallel Computation," Proc. Fourth ACM SIGPLAN Symp. Principles and Practices of Parallel Programming, May 1993.

- A. Alexandrov, M. Ionescu, K.E. Schauser, and C. Scheiman, [3] "LogGP: Incorporating Long Messages into the LogP Model," Proc. Symp. Parallel Algorithms and Architectures '95, July 1995.

- J. Babb, R. Tessier, M. Dahl, S. Hanono, D. Hoki, and A. Agarwal, [4] 'Logic Emulation with Virtual Wires," IEEE Trans. Computer-Aided Design, vol. 16, no. 6, pp. 609-626, June 1997.

- J.C. Eble III, "A Generic System Simulator with Novel On-Chip [5] Cache and Throughput Models for Gigascale Integration," PhD thesis, Georgia Inst. of Technology, Nov. 1998.

- J.M. Mulder, N.T. Quach, and M.J. Flynn, "An Area Model for On-Chip Memories and Its Application," *IEEE J. Solid-State* [6] Circuits, vol. 26, no. 2, pp. 98-106, Feb. 1991.

- H.B. Bakoglu, Circuits, Interconnects and Packaging for VLSI. [7] Reading, Mass.: Addison-Wesley, 1990.

- M.I. Frank, A. Agarwal, and M.K. Vernon, "LoPC:Modeling [8] Contention in Parallel Algorithms," Proc. Sixth ACM SIGPLAN Symp. Principles and Practice of Parallel Programming, June 1997. C.A. Moritz and M.I. Frank, "LoGPC: Modeling Network

- [9] Contention in Message-Passing Programs," IEEE Trans. Parallel and Distributed Systems, vol. 12, no. 4, 2001.

- [10] D. Brooks, V. Tiwari, and M. Martonosi, "Wattch: A Framework for Architectural-Level Power Analysis and Optimizations," Proc. 27th Int'l Symp. Computer Architecture, June 2000.

- [11] A. Alexandrov, M. Jonescu, K.E. Schauser, and C. Scheiman, "LogGP: Incorporating Long Messages into the LogP Model," Proc. Symp. Parallel Algorithms and Architectures '95, July 1995.

- [12] D. Yeung, W.J. Dally, and A. Agarwal, "How to Choose the Grain Size of a Parallel Computer," MIT/LCS Technical Report MIT-LCS-TR-739, Feb. 1994.

- [13] C.L. Seitz, N.J. Boden, J. Seizovic, and W.-K. Su, "The Design of the Caltech Mosaic C Multicomputer," Proc. 1993 Symp. Research on Integrated Systems, pp. 1-22, 1993.

- [14] H. Nishi, K.-I. Anjo, T. Kudoh, and H. Amano, "The RDT Router Chip: A Versatile Router for Supporting Shared Memory," Special Issue on Architecture, Algorithms and Networks for Massively Parallel Computing, IEICE, vol. E00-A, no. 1, Jan. 1997.

- [15] CPU Info Center, http://bwrc.eecs.berkeley.edu/CIC/, 2001.

[16] P.R. Nuth and W.J. Dally, "The J-Machine Network," *Proc.* 1992 IEEE Int'l Conf. Computer Design: VLSI in Computers and Processors, pp. 420-423, Óct. 1992.

- C.L. Seitz and W.-K. Su, "A Family of Routing and Communica-tion Chips Based on the Mosaic," *Proc.* 1993 Symp. Research on [17] Integrated Systems, pp. 320-337, 1993.

- [18] H.T. Kung, "Memory Requirements for Balanced Computer Architectures," Proc. Int'l Symp. Computer Architecture, ISCA, pp. 49-54, 1986.

- [19] T.J. Holman and L. Snyder, "Architectural Tradeoffs in Parallel Computer Design," Proc. 1989 Decennial Caltech Conf. Advanced Research in VLSI, pp. 317-334, Mar. 1989.

- [20] Paul Chow, The MIPS-X RISC Microprocessor. Kluwer Academic, Aug. 1989.

- [21] W.J. Dally, "Architecture of a Message-Driven Processor," Proc. 14th Ann. Symp. Computer Architecture, pp. 189-196, June 1987.

- W.J. Dally and C.L. Seitz, "The Torus Routing Chip," Distributed Computing, vol. 1, pp. 187-196, 1986. [22]

- [23] A. Agarwal, D. Chaiken, G. D'Souza, K. Johnson, D. Kranz, J. Kubiatowicz, K. Kurihara, B.-H. Lim, G. Maa, D. Nussbaum, M. Parkin, and D. Yeung, "The MIT Alewife Machine: A Large-Scale Distributed-Memory Multiprocessor," Proc. Workshop Scalable Shared Memory Multiprocessors, 1991, (also appears as MIT/ LCS Memo TM-454, 1991).

- [24] W.J. Dally et al., "The J-Machine: A Fine-Grain Concurrent Computer," Proc. Int'l Federation for Information Processing 11th World Congress, pp. 1147-1153, 1989.

- Thinking Machines Corp., CM5 Technical Summary. Cambridge, [25] Mass., Öct. 1991.

- CRAY T3D System Architecture Overview, Revision 1.C. Cray [26] Research, Inc., Sept. 1993.

- [27] K. Diefendorff and M. Allen, "Organization of the Motorola 88110 Superscalar RISC Microprocessor," IEEE Micro, vol. 2, no. 2, pp. 40-63, Apr. 1992.

- [28] D. Allison and M. Slater, "National Unveils Superscalar RISC Processor," Microprocessor Report, vol. 5, no. 3, Feb. 1991.

- D. Dobberpuhl et al., "A 200 Mhz 64b Dual-Issue Micro-[29] processor," Proc. IEEE Solid State Circuits Conf., vol. 35, pp. 106-107, Feb. 1992.

Csaba Andras Moritz obtained the PhD degree in computer systems from the Royal Institute of Technology, Stockholm, Sweden in 1998 and the MSEE degree from the Technical University Cluj, Romania in 1985. He is an associate professor in the Department of Electrical and Computer Engineering University of Massachusetts, Amherst. From 1997 to 2000, he was a research scientist at MIT, Laboratory for Computer Science. He has consulted for

several technology companies in Scandinavia and held industrial positions ranging from chief technology officer to founder. His research interests include modeling, computer architecture, compilers, and scalability issues in distributed systems.

Donald Yeung received the BS degree from Stanford University and the MS and PhD degrees from the Massachusetts Institute of Technology. He is currently an assistant professor at the University of Maryland at College Park. His research interests are in the areas of computer architecture, performance evaluation of computer systems, and the interaction between architectures, operating systems, and applications. He is particularly interested in

memory system issues for both uniprocessor and multiprocessor architectures. Currently, he is investigating techniques to bridge the widening gap between processor and memory performance.

Anant Agarwal received the BTech degree in electrical engineering from the Indian Institute of Technology, Madras, India in 1982 and the MS and PhD degrees in electrical engineering from Stanford University, Stanford, California in 1984 and 1987, respectively. He is currently with the Laboratory for Computer Science at the Massachusetts Institute of Technology, Cambridge as a professor of electrical engineering and computer science. At Stanford, he participated

in the MIPS and MIPS-X projects. He led the Alewife project at MIT which designed and implemented a large-scale cache-coherent multiprocessor. He currently codirects the Raw and Oxygen projects. Raw is developing a software-exposed VLSI processor architecture that exposes its wires to the compiler. Oxygen is building a pervasive computing environment in which humans interact with computation using speech and vision.

> For further information on this or any computing topic, please visit our Digital Library at http://computer.org/publications/dlib.